随着雷达、电子侦察与对抗、通信等领域技术的发展,对频率源提出了越来越高的要求,主要表现在高频率、低相噪、低杂散、小步进、宽频带、小体积等方面。频率合成技术作为系统实现高性能指标的关键技术之一,包括四种合成方式:直接模拟式频率合成、锁相频率合成(PLL)、直接数字式频率合成(DDS)和混合式频率合成(DDS+PLL)

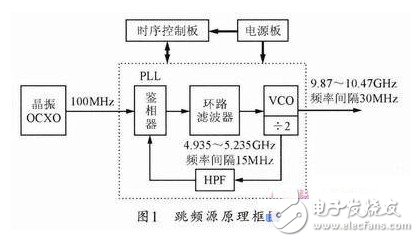

根据所列指标,如果采用直接模拟式虽然相噪、杂散、跳频时间等指标得以保证,但由于所需设备量大,导致体积大、成本高。DDS+PLL合成方式包括DDS激励PLL的方式、DDS内插入PLL做分频器以及DDS与PLL混频的方式。DDS激励PLL做分频器的方式由于DDS最大输出频率不高,需要多次倍频从而恶化相噪,难以满足系统要求DDS与PLL环外混频的方式由于输出信号的带宽和杂散主要取决于 DDS而难以满足系统要求,而DDS内插PLL作为分频器的方式得到的信号杂散较低,频率分辨率小且能做到较宽的频带,但是时钟频率较高的DDS价格昂贵。采用锁相环合成,杂散性能与相位噪声性能较好,可实现的工作频带宽,但频率切换速度较慢,跳频时间较长。由于系统并没有对频率切换速度提出过高要求,因此从价格方面考虑,我们采用锁相频率合成技术,基于低相噪锁相环芯片HMC704LP4设计该跳频源。其原理框图如图1所示。

选用100MHz OCXO晶振作参考输入信号,采用Hittite公司的小数分频数字锁相环HMC704LP4产生9.87~10.47 GHz、频率间隔为30 MHz的信号。锁相环接收来自时序控制板的控制信号,通过对鉴相器的内部寄存器进行控制,产生所需频点。由于输出频率不能被30 MHz整除,如果选择整数模式则鉴相频率应为10 MHz,分频比N较大,噪声会以20 lgN恶化。因此我们采用小数分频模式,鉴相频率为100 MHz,提高了相噪性能,同时由于HMC704LP4采用Delta-sigma调制技术改善了分数杂散性能,使得输出信号的杂散满足要求。

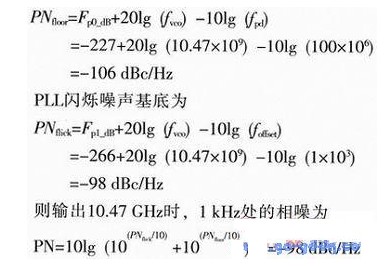

锁相环系统的相位噪声来源于参考输入、反馈分频1/N、电荷泵和VCO.存环路带宽内,参考输入的相位噪声和N分频的噪声占很大比例,电荷泵的相位噪声也很重要。环路带宽外的相噪主要由VCO的相噪决定。

跳频源杂散包括锁相环的鉴相泄露、小数杂散以及电磁兼容等方面带来的杂散。在小数模式下,由于 VCO的输出频率与鉴相频率不是整数倍的关系,所以输出信号的杂散由VCO频率和鉴相频率谐波的交互调产生。小数杂散位于输出频率 [fvco-(nFPD+fpdd/m)]处,其中fpd为鉴相频率,d《m,m为小数杂散阶数,大于四阶的小数杂散已经非常小可忽略不计。由理论计算可得距离输出频率最近的杂散为7 MHz处。杂散都在环路带宽之外,环路滤波器可将其滤除保证杂散-70 dBc,满足要求。

HMC704LP4是Hittite公司2011年4月推出的一款低相噪小数分频锁相环芯片,其最高工作频率可达8 GHz,具有整数模式和小数模式,包括鉴相器,精密电荷泵,参考分频器R,可编程分频器N,Delta-sigma调制器以及缓冲放大电路等。

(3)最高参考输入频率高达350 MHz,在整数模式下鉴相频率最高为115 MHz,在小数模式下鉴相频率最高为100 MHz,最小可至DC;

(4)该芯片有八个供电引脚,其中电荷泵部分的供电电压为5 V,其他供电均为3.3 V;5 V电流典型值6 mA;3.3 V电流典型值52 mA;

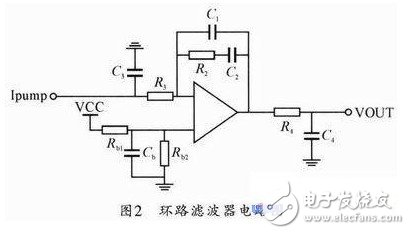

环路滤波器设计是锁相环设计的关键部分。环路滤波器处于鉴相器和VCO之间,可以滤除来自晶振的噪声,鉴相器本身的输出噪声和载频分量,滤除杂散,还可以滤除来自VCO的噪声,但最重要的是建立起环路的动态特性。

滤波器设计时带宽需要折中考虑。带宽小,呵降低近端相噪,环路锁定时间长。带宽大,环路锁定时间短,但会引入参考杂散。本设计借助于Hittite PLL Design设计滤波器。该软件是Hittite公司推出的锁相环辅助设计软件,可以仿真锁相环的相噪特性、环路特性等。可通过修改环路带宽、相位裕量、零极点等来修改各参数值。本系统采用四阶有源滤波器。电路如图2所示。

本跳频源输出X波段频率,电路基板采用ROGERS 4350B (介电常数3.48,厚度0.508 mm),各部分电路必须具有良好隔离和屏蔽。整个电路放在铝腔体中,以保证内部和外部的电磁隔离。腔体分为上下两层。锁相环电路放在上层。电源板和控制电路放在下层。为了获得好的相噪指标,对系统的供电设计要特别注意。系统供电包括+15V、+5 V和+3.3 V.+15 V、+5 V由电源板经过滤波后直接给锁相环电路供电。+3.3 V由+5 V经LDO产生。各+5 V电源之间用磁珠进行隔离,各+3.3 V电源间也果用磁珠进行隔离。

HMC704寄存器较多,配置起来比较复杂,是设计难点之一。我们采用ALTEra公司的 FPCAEP1C3T14417对HMC704进行配置。通过SPI串口用开放模式配置,可以减少配置时间,进一步减小跳频时间。利用SCLK上升沿将数据、寄存器地址、芯片地址码依次通过SDI送给PLL内部的移位寄存器后,令SEN变为高电平将移位寄存器中的数据所存至相应锁存器中,锁相环进入相应频率锁定过程。跳频时,改变频点只用改变N整数寄存器和N小数寄存器即可。

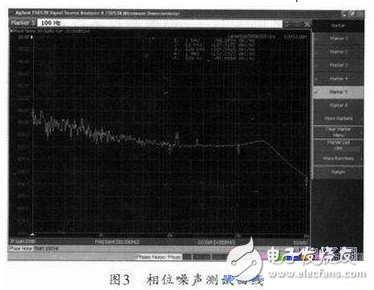

采用Agilent频谱仪N9030A和信号源分析仪E5052B分别对该跳频源的杂散、相噪和跳频时间进行测试。相位噪声测试曲线 GHz,相噪指标为-96dBc/Hz@1kHz;杂散测试如图4、图5所示,测试频率为10.44 GHz,图4为近端杂散、图5为远端杂散。杂散优于-70dBc.跳频时间测试的是9.9 GHz到10.93 GHz的跳频时间,约为36 s.

该跳频源高于指标要求,体积为60x40×19mm3,且性能稳定可靠。经验证该设计方案可应用于同类型的频率频率源设计当中去,具有实际的指导意义。